四川益丰电子科技有限公司

Sichuan YiFeng Electronic Science & Technology Co., LTD

## 产品介绍

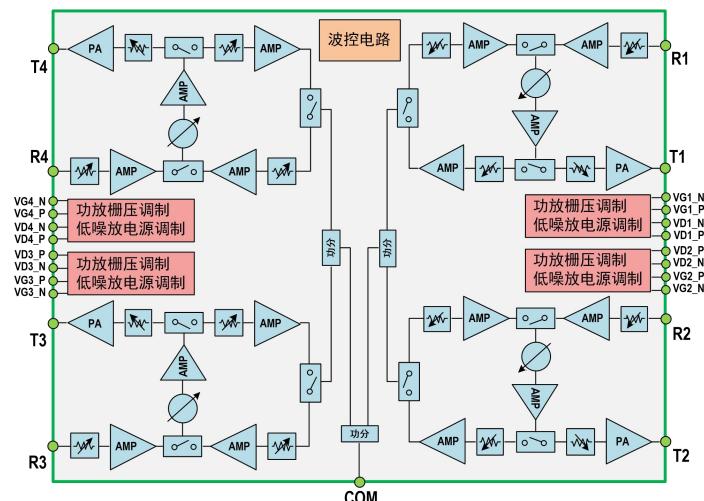

YCC72-0513C1 是一款宽带四通道多功能芯片。工作频率范围 5GHz~13GHz，芯片内部集成低噪声放大器，功率放大器，射频前端开关，6 位数控衰减器，6 位数控移相器，功分器，波束控制，功放栅压调制，低噪放电源调制等模块，可提供最大 31.5dB 的衰减范围，步进 0.5dB，以及 360° 的移相范围，步进 5.6°。

## 应用领域

- 雷达

- 通信

YCC72-0513C1 芯片模块示意图

## 关键技术指标

- 工作电源电压: 3.3V

- 工作频率范围: 5GHz~13GHz

- 6 位衰减控制位, 步进 0.5dB

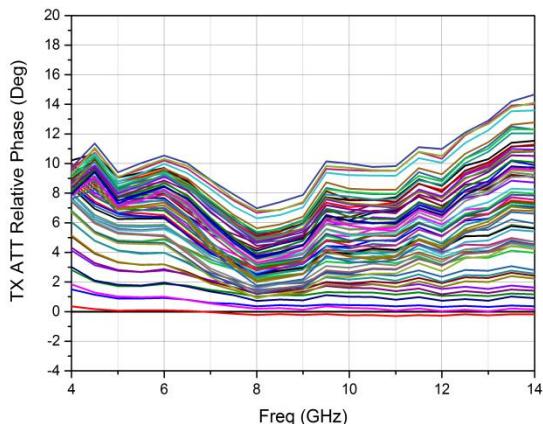

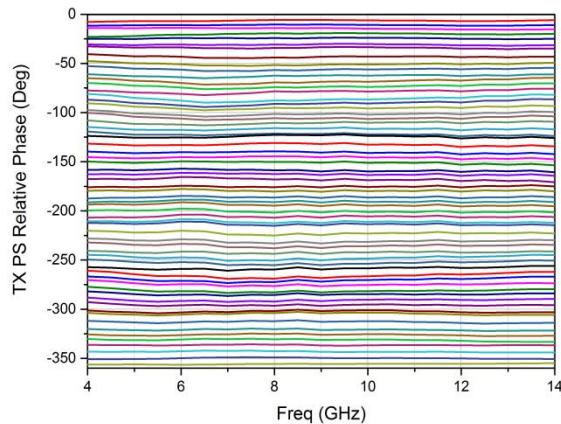

- 6 位移相控制位, 步进 5.6°

- 接收增益: 6dB (Rn 端口到 COM 端口)

- 发射增益: 17dB (COM 端口到 Tn 端口)

- 收发带内增益平坦度: 3dB

- 端口驻波比 VSWR: 1.8

- 接收噪声系数 NF: 13dB

- 接收输入 Pin-1dB: 0dBm

- 发射输出 Po-1dB: 17dBm

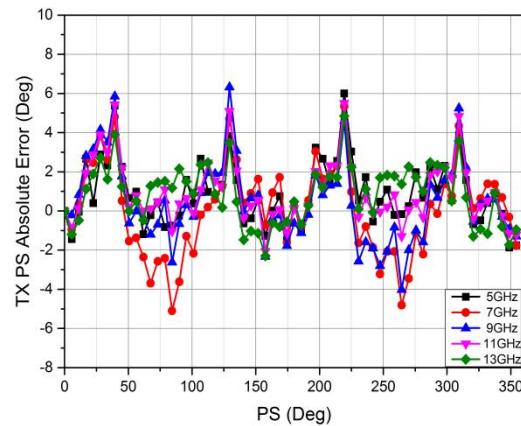

- RMS 相移误差: <3°

- 移相时幅度一致性: <±0.8dB

- 衰减精度: <0.2+5%Ai

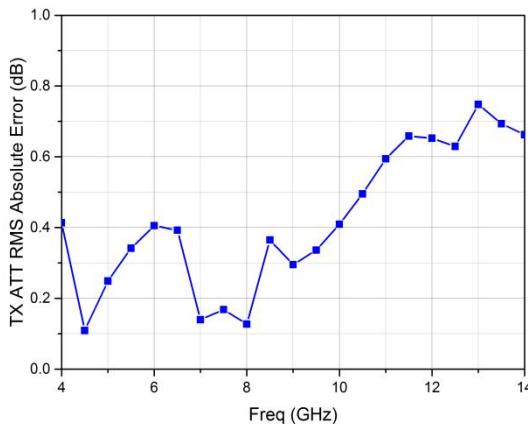

- RMS 衰减误差: <0.8dB

- 衰减附加相移: <15°

- 收发切换时间: <100ns

- 单通道工作电流: 85mA/90(170)mA/2mA@接收/静态 (Po-1dB) 发射/负载

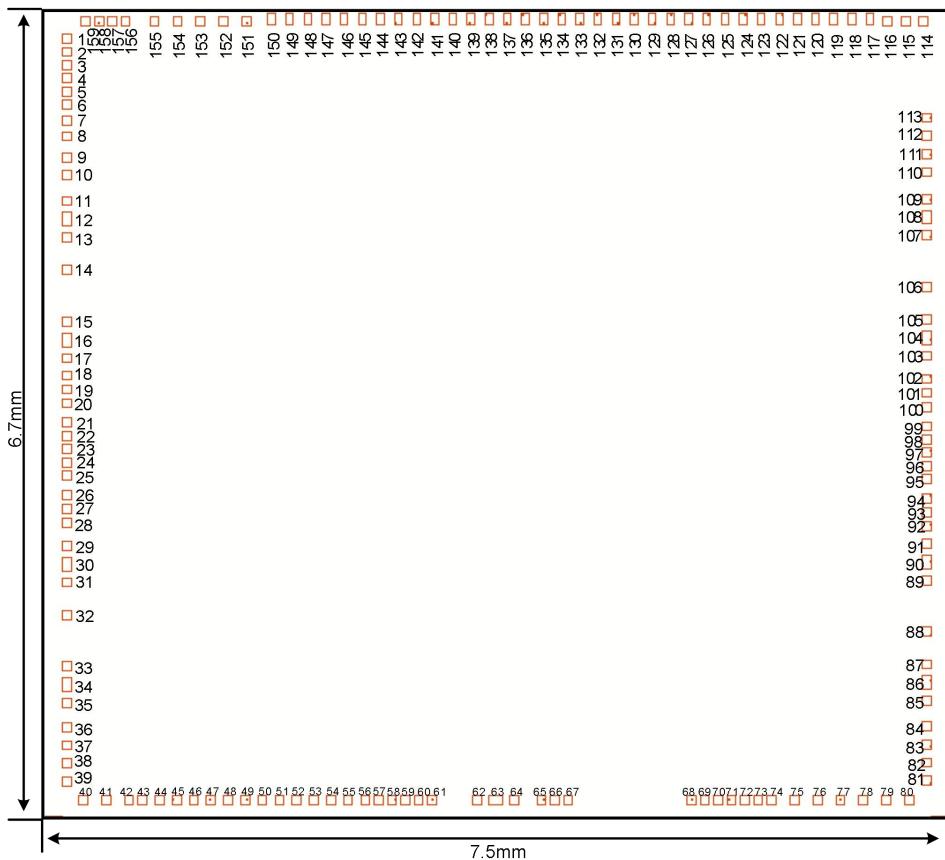

- 裸芯尺寸: 7.5mm×6.7mm

- 工艺: SiGe BiCMOS

## 电气特性

基本电性能

| 参数              | 条件            | 最小值  | 典型值 | 最大值 | 单位  |

|-----------------|---------------|------|-----|-----|-----|

| 频率范围            |               | 5    |     | 13  | GHz |

| 接收线性增益          | Rn 端口到 COM 端口 |      | 6   |     | dB  |

| 发射线性增益          | COM 端口到 Tn 端口 |      | 17  |     | dB  |

| 带内增益平坦度         |               |      | 3   |     | dB  |

| 端口驻波比           |               |      | 1.8 |     | —   |

| 接收噪声系数          |               |      | 13  |     | dB  |

| 接收输入 P-1dB      |               |      | 0   |     | dBm |

| 发射输出 P-1dB      |               |      | 17  |     | dBm |

| 发射输出 Psat       |               |      | 19  |     | dBm |

| RMS 相移误差        |               |      |     | 3   | Deg |

| 移相幅度一致性         |               | -0.8 |     | 0.8 | dB  |

| RMS 衰减误差        |               |      |     | 0.8 | dB  |

| 衰减附加相移          |               | -2   |     | 15  | Deg |

| 收发切换时间          |               |      |     | 100 | ns  |

| 单通道接收电流         |               |      | 85  |     | mA  |

| 单通道静态发射电流       |               |      | 90  |     | mA  |

| 单通道 Po-1dB 发射电流 |               | 150  | 170 | 200 | mA  |

| 单通道负载态电流        |               |      | 2   |     | mA  |

数字端口电参数

| 参数      | 符号              | 条件                                                 | 最小值     | 最大值 | 单位 |

|---------|-----------------|----------------------------------------------------|---------|-----|----|

| 输入高电平电压 | VIH             | VCC = 2.7 V to 3.6 V,                              | 1.7     |     | V  |

| 输入低电平电压 | VIL             | VCC = 2.7 V to 3.6 V,                              |         | 0.8 | V  |

| 输入高电平电流 | I <sub>IH</sub> | VCC = 2.7 V to 3.6 V,                              | -500    | 500 | uA |

| 输入低电平电流 | I <sub>IL</sub> | VCC = 2.7 V to 3.6 V,                              | -500    | 500 | uA |

| 输出高电平电压 | V <sub>OH</sub> | VCC = 2.7 V to 3.6 V,<br>I <sub>OH</sub> = -100 uA | VCC-0.2 | VCC | V  |

| 输出高电平电压 | V <sub>OH</sub> | VCC = 2.7 V<br>I <sub>OH</sub> = -4mA              | 2.4     | VCC | V  |

| 输出低电平电压 | V <sub>OL</sub> | VCC = 2.7 V to 3.6 V,<br>I <sub>OL</sub> = 100 uA  | 0       | 0.2 | V  |

| 输出低电平电压 | V <sub>OL</sub> | VCC = 2.7 V, I <sub>OL</sub> = 4mA                 | 0       | 0.4 | V  |

## 极限参数

|          |           |

|----------|-----------|

| 最大电源电压   | 3.6V      |

| 最大射频输入功率 | 20dBm     |

| 存储温度     | -65~150°C |

| 使用温度     | -55~125°C |

**注意:** 对以上所列的最大极限值, 如果器件工作在超过此极限值的环境中, 很可能会对器件造成永久性破坏。

在实际运用中, 最好不要使器件工作在此极限值或超过此极限值的环境中。

## ESD保护

YCC72-0513C1 防静电等级(人体模式 HBM)至少为 Class 2:  $\geq 2000V$ 。当拿取时, 要采取合适的 ESD 保护措施, 以免造成性能下降或功能失效。

## 管脚配置

芯片焊盘布局图

芯片焊盘功能信息表

| 序号 | 名称      | X 坐标<br>um | Y 坐标<br>um | 焊盘大<br>小<br>um×um | 功能                                                                                                                      |

|----|---------|------------|------------|-------------------|-------------------------------------------------------------------------------------------------------------------------|

| 1  | NC      | 191.4      | 6460.51    | 74×74             | 悬空                                                                                                                      |

| 2  | NC      | 191.4      | 6350.51    | 74×74             | 悬空                                                                                                                      |

| 3  | NC      | 191.4      | 6240.51    | 74×74             | 悬空                                                                                                                      |

| 4  | NC      | 191.4      | 6130.51    | 74×74             | 悬空                                                                                                                      |

| 5  | NC      | 191.4      | 6020.51    | 74×74             | 悬空                                                                                                                      |

| 6  | NC      | 191.4      | 5910.51    | 74×74             | 悬空                                                                                                                      |

| 7  | RX_4    | 191.4      | 5780.51    | 74×74             | 通道 4 RX 控制输出                                                                                                            |

| 8  | TX0_4   | 191.4      | 5650.51    | 74×74             | 通道 4 TX0 控制输出                                                                                                           |

| 9  | TX1_4   | 191.4      | 5475.6     | 74×74             | 通道 4 TX1 控制输出                                                                                                           |

| 10 | TXD_4   | 191.4      | 5325.6     | 74×74             | 通道 4 TXD 控制输出                                                                                                           |

| 11 | GND     | 191.4      | 5112.11    | 74×74             | 地                                                                                                                       |

| 12 | T4      | 191.4      | 4960.91    | 74×114            | 通道 4 发射链路输出                                                                                                             |

| 13 | GND     | 191.4      | 4809.71    | 74×74             | 地                                                                                                                       |

| 14 | VDD33   | 191.4      | 4539.71    | 74×74             | 通道 4 电源 3.3V                                                                                                            |

| 15 | GND     | 191.4      | 4112.11    | 74×74             | 地                                                                                                                       |

| 16 | R4      | 191.4      | 3960.91    | 74×114            | 通道 4 接收链路输入                                                                                                             |

| 17 | GND     | 191.4      | 3809.71    | 74×74             | 地                                                                                                                       |

| 18 | VG4_N   | 191.4      | 3666.82    | 74×74             | 通道 4 栅压驱动输出, 驱动能力±20mA, 受通道 4 的波控输出 TX1 控制。TX1 为高时, VG4_N 输出负压 VO1, VG4_P 输出-5V; TX1 为低时, VG4_N 输出-5V, VG4_P 输出负压 VO1   |

| 19 | VG4_P   | 191.4      | 3550.82    | 74×74             |                                                                                                                         |

| 20 | VD4_N   | 191.4      | 3434.82    | 74×74             | 通道 4 低噪放电源调制输出, 驱动能力>100mA, 受通道 4 的波控输出 RX 控制。RX 为高时, VD4_N 输出高电平(VDD5/33), VD4_P 输出 0; RX 为低时, VD4_N 输出 0, VD4_P 输出高电平 |

| 21 | VD4_P   | 191.4      | 3274.82    | 74×74             |                                                                                                                         |

| 22 | VDD33   | 191.4      | 3164.82    | 74×74             | 通道 4 电源 3.3V                                                                                                            |

| 23 | VDD5/33 | 191.4      | 3054.82    | 74×74             | 通道 3 和通道 4 低噪放电源调制电路的电源, 5V 或 3.3V                                                                                      |

| 24 | VDD33   | 191.4      | 2944.82    | 74×74             | 通道 3 电源 3.3V                                                                                                            |

| 25 | VD3_P   | 191.4      | 2834.82    | 74×74             | 通道 3 低噪放电源调制输出, 驱动能力>100mA, 受通道 3 的波控输出 RX 控制。RX 为高时, VD3_N 输出高电平(VDD5/33), VD3_P 输出 0; RX 为低时, VD3_N 输出 0, VD3_P 输出高电平 |

| 26 | VD3_N   | 191.4      | 2674.82    | 74×74             |                                                                                                                         |

| 27 | VG3_P   | 191.4      | 2558.82    | 74×74             | 通道 3 栅压驱动输出, 驱动能力±20mA, 受通道 3 的波控输出 TX1 控制。TX1 为高时, VG3_N 输出负压 VO1, VG3_P 输出-5V; TX1 为低时, VG3_N 输出-5V, VG3_P 输出负压 VO1   |

| 28 | VG3_N   | 191.4      | 2442.82    | 74×74             |                                                                                                                         |

| 29 | GND     | 191.4      | 2252.11    | 74×74             | 地                                                                                                                       |

YCC72-0513C1

数据手册

|    |         |         |         |        |                                                    |

|----|---------|---------|---------|--------|----------------------------------------------------|

| 30 | T3      | 191.4   | 2100.91 | 74×114 | 通道 3 发射链路输出                                        |

| 31 | GND     | 191.4   | 1949.71 | 74×74  | 地                                                  |

| 32 | VDD33   | 191.4   | 1679.71 | 74×74  | 通道 3 电源 3.3V                                       |

| 33 | GND     | 191.4   | 1252.11 | 74×74  | 地                                                  |

| 34 | R3      | 191.4   | 1100.91 | 74×114 | 通道 3 接收链路输入                                        |

| 35 | GND     | 191.4   | 949.71  | 74×74  | 地                                                  |

| 36 | TXD_3   | 191.4   | 749.49  | 74×74  | 通道 3 TXD 控制输出                                      |

| 37 | TX1_3   | 191.4   | 599.49  | 74×74  | 通道 3 TX1 控制输出                                      |

| 38 | TX0_3   | 191.4   | 449.49  | 74×74  | 通道 3 TX0 控制输出                                      |

| 39 | RX_3    | 191.4   | 299.49  | 74×74  | 通道 3 RX 控制输出                                       |

| 40 | AC3_<1> | 328.12  | 141.4   | 74×74  | 增益调节, 默认悬空, 接地时通道 3 增益调低 0.5dB                     |

| 41 | AC3_<2> | 518.12  | 141.4   | 74×74  | 增益调节, 默认悬空, 接地时通道 3 增益调低 1dB                       |

| 42 | AC3_<3> | 708.12  | 141.4   | 74×74  | 增益调节, 默认悬空, 接地时通道 3 增益调高 0.5dB                     |

| 43 | A5_<5>  | 818.12  | 141.4   | 74×74  | 通道 5 增益控制信号输出 bit5                                 |

| 44 | A5_<4>  | 959.92  | 141.4   | 74×74  | 通道 5 增益控制信号输出 bit4                                 |

| 45 | A5_<3>  | 1101.72 | 141.4   | 74×74  | 通道 5 增益控制信号输出 bit3                                 |

| 46 | A5_<2>  | 1243.52 | 141.4   | 74×74  | 通道 5 增益控制信号输出 bit2                                 |

| 47 | A5_<1>  | 1385.32 | 141.4   | 74×74  | 通道 5 增益控制信号输出 bit1                                 |

| 48 | A5_<0>  | 1527.12 | 141.4   | 74×74  | 通道 5 增益控制信号输出 bit0                                 |

| 49 | P5_<5>  | 1668.92 | 141.4   | 74×74  | 通道 5 相位控制信号输出 bit5                                 |

| 50 | P5_<4>  | 1810.72 | 141.4   | 74×74  | 通道 5 相位控制信号输出 bit4                                 |

| 51 | P5_<3>  | 1952.52 | 141.4   | 74×74  | 通道 5 相位控制信号输出 bit3                                 |

| 52 | P5_<2>  | 2094.32 | 141.4   | 74×74  | 通道 5 相位控制信号输出 bit2                                 |

| 53 | P5_<1>  | 2236.12 | 141.4   | 74×74  | 通道 5 相位控制信号输出 bit1                                 |

| 54 | P5_<0>  | 2377.92 | 141.4   | 74×74  | 通道 5 相位控制信号输出 bit0                                 |

| 55 | RX_5    | 2519.72 | 141.4   | 74×74  | 通道 5 RX 控制输出                                       |

| 56 | TX0_5   | 2662.12 | 141.4   | 74×74  | 通道 5 TX0 控制输出                                      |

| 57 | TX1_5   | 2772.12 | 141.4   | 74×74  | 通道 5 TX1 控制输出                                      |

| 58 | TXD_5   | 2882.12 | 141.4   | 74×74  | 通道 5 TXD 控制输出                                      |

| 59 | VDD33   | 2992.12 | 141.4   | 74×74  | 负压及逻辑电路 3.3V 电源                                    |

| 60 | VO1     | 3102.12 | 141.4   | 74×74  | 负压 VO1, 片外接 1uF 以上的稳压电容                            |

| 61 | VEE     | 3212.12 | 141.4   | 74×74  | 负压电路-5V 电源                                         |

| 62 | GND     | 3589.71 | 141.4   | 74×74  | 地                                                  |

| 63 | COM     | 3740.91 | 141.4   | 114×74 | 公共端口                                               |

| 64 | GND     | 3892.11 | 141.4   | 74×74  | 地                                                  |

| 65 | VG_P0   | 4120.47 | 141.4   | 74×74  | 负压输出 VO1 调节, 默认高电平, P2,P1,P0 三位:                   |

| 66 | VG_P1   | 4230.47 | 141.4   | 74×74  | 000:-2.4V,001:-2.3V,010:-2.2V,011:-2.2V,011:-2.1V, |

| 67 | VG_P2   | 4340.47 | 141.4   | 74×74  | 100:-2.0V,101:-1.9V,110:-1.8V,111:-1.7V            |

| 68 | NC      | 5361.97 | 141.4   | 74×74  | 悬空                                                 |

| 69 | NC      | 5471.97 | 141.4   | 74×74  | 悬空                                                 |

| 70 | NC      | 5581.97 | 141.4   | 74×74  | 悬空                                                 |

| 71 | NC      | 5691.97 | 141.4   | 74×74  | 悬空                                                 |

YCC72-0513C1

数据手册

|     |         |         |         |        |                                                                                                                         |

|-----|---------|---------|---------|--------|-------------------------------------------------------------------------------------------------------------------------|

| 72  | NC      | 5801.97 | 141.4   | 74×74  | 悬空                                                                                                                      |

| 73  | NC      | 5911.97 | 141.4   | 74×74  | 悬空                                                                                                                      |

| 74  | NC      | 6021.97 | 141.4   | 74×74  | 悬空                                                                                                                      |

| 75  | NC      | 6211.97 | 141.4   | 74×74  | 悬空                                                                                                                      |

| 76  | NC      | 6401.97 | 141.4   | 74×74  | 悬空                                                                                                                      |

| 77  | NC      | 6591.97 | 141.4   | 74×74  | 悬空                                                                                                                      |

| 78  | AC2_<3> | 6781.88 | 141.4   | 74×74  | 增益调节, 默认悬空, 接地时通道 2 增益调高 0.5dB                                                                                          |

| 79  | AC2_<2> | 6971.88 | 141.4   | 74×74  | 增益调节, 默认悬空, 接地时通道 2 增益调低 1dB                                                                                            |

| 80  | AC2_<1> | 7161.88 | 141.4   | 74×74  | 增益调节, 默认悬空, 接地时通道 2 增益调低 0.5dB                                                                                          |

| 81  | RX_2    | 7308.6  | 304.4   | 74×74  | 通道 2 RX 控制输出                                                                                                            |

| 82  | TX0_2   | 7308.6  | 454.4   | 74×74  | 通道 2 TX0 控制输出                                                                                                           |

| 83  | TX1_2   | 7308.6  | 604.4   | 74×74  | 通道 2 TX1 控制输出                                                                                                           |

| 84  | TXD_2   | 7308.6  | 754.4   | 74×74  | 通道 2 TXD 控制输出                                                                                                           |

| 85  | GND     | 7308.6  | 967.89  | 74×74  | 地                                                                                                                       |

| 86  | T2      | 7308.6  | 1119.09 | 74×114 | 通道 2 发射链路输出                                                                                                             |

| 87  | GND     | 7308.6  | 1270.29 | 74×74  | 地                                                                                                                       |

| 88  | VDD33   | 7308.6  | 1540.29 | 74×74  | 通道 2 电源 3.3V                                                                                                            |

| 89  | GND     | 7308.6  | 1967.89 | 74×74  | 模拟地                                                                                                                     |

| 90  | R2      | 7308.6  | 2119.09 | 74×114 | 通道 2 接收链路输入                                                                                                             |

| 91  | GND     | 7308.6  | 2270.29 | 74×74  | 模拟地                                                                                                                     |

| 92  | VG2_N   | 7308.6  | 2413.18 | 74×74  | 通道 2 栅压驱动输出, 驱动能力±20mA, 受通道 2 的波控输出 TX1 控制。TX1 为高时, VG2_N 输出负压 VO1, VG2_P 输出-5V; TX1 为低时, VG2_N 输出-5V, VG2_P 输出负压 VO1   |

| 93  | VG2_P   | 7308.6  | 2529.18 | 74×74  |                                                                                                                         |

| 94  | VD2_N   | 7308.6  | 2645.18 | 74×74  | 通道 2 低噪放电源调制输出, 驱动能力>100mA, 受通道 2 的波控输出 RX 控制。RX 为高时, VD2_N 输出高电平(VDD5/33), VD2_P 输出 0; RX 为低时, VD2_N 输出 0, VD3_P 输出高电平 |

| 95  | VD2_P   | 7308.6  | 2805.18 | 74×74  |                                                                                                                         |

| 96  | VDD33   | 7308.6  | 2915.18 | 74×74  | 通道 2 电源 3.3V                                                                                                            |

| 97  | VDD5/33 | 7308.6  | 3025.18 | 74×74  | 通道 1 和通道 2 低噪放电源调制电路的电源, 5V 或 3.3V                                                                                      |

| 98  | VDD33   | 7308.6  | 3135.18 | 74×74  | 通道 1 电源 3.3V                                                                                                            |

| 99  | VD1_P   | 7308.6  | 3245.18 | 74×74  | 通道 1 低噪放电源调制输出, 驱动能力>100mA, 受通道 1 的波控输出 RX 控制。RX 为高时, VD1_N 输出高电平(VDD5/33), VD1_P 输出 0; RX 为低时, VD1_N 输出 0, VD1_P 输出高电平 |

| 100 | VD1_N   | 7308.6  | 3405.18 | 74×74  |                                                                                                                         |

| 101 | VG1_P   | 7308.6  | 3521.18 | 74×74  | 通道 1 栅压驱动输出, 驱动能力±20mA, 受通道 1 的波控输出 TX1 控制。TX1 为高时, VG1_N 输出负压 VO1, VG1_P 输出-5V; TX1 为低时, VG1_N 输出-5V, VG1_P 输出负压 VO1   |

| 102 | VG1_N   | 7308.6  | 3637.18 | 74×74  |                                                                                                                         |

| 103 | GND     | 7308.6  | 3827.89 | 74×74  | 模拟地                                                                                                                     |

| 104 | T1      | 7308.6  | 3979.09 | 74×114 | 通道 1 发射连路输出                                                                                                             |

| 105 | GND     | 7308.6  | 4130.29 | 74×74  | 模拟地                                                                                                                     |

| 106 | VDD33   | 7308.6  | 4400.29 | 74×74  | 通道 1 电源 3.3V                                                                                                            |

YCC72-0513C1

数据手册

|     |           |         |         |        |                                            |

|-----|-----------|---------|---------|--------|--------------------------------------------|

| 107 | GND       | 7308.6  | 4827.89 | 74×74  | 模拟地                                        |

| 108 | R1        | 7308.6  | 4979.09 | 74×114 | 通道 1 接收链路输入                                |

| 109 | GND       | 7308.6  | 5130.29 | 74×74  | 模拟地                                        |

| 110 | TXD_1     | 7308.6  | 5352.11 | 74×74  | 通道 1 TXD 控制输出                              |

| 111 | TX1_1     | 7308.6  | 5502.11 | 74×74  | 通道 1 TX1 控制输出                              |

| 112 | TX0_1     | 7308.6  | 5652.11 | 74×74  | 通道 1 TX0 控制输出                              |

| 113 | RX_1      | 7308.6  | 5802.11 | 74×74  | 通道 1 RX 控制输出                               |

| 114 | AC1_<1>   | 7280.69 | 6604.4  | 74×74  | 增益调节, 默认悬空, 接地时通道 1 增益调低 0.5dB             |

| 115 | AC1_<2>   | 7130.69 | 6604.4  | 74×74  | 增益调节, 默认悬空, 接地时通道 1 增益调低 1dB               |

| 116 | AC1_<3>   | 6980.69 | 6604.4  | 74×74  | 增益调节, 默认悬空, 接地时通道 1 增益调高 0.5dB             |

| 117 | VDD33     | 6836.69 | 6621.5  | 62×95  | 波控电路 3.3V 电源                               |

| 118 | NC        | 6686.69 | 6621.5  | 62×95  | 悬空                                         |

| 119 | NC        | 6536.69 | 6621.5  | 62×95  | 悬空                                         |

| 120 | NC        | 6386.69 | 6621.5  | 62×95  | 悬空                                         |

| 121 | NC        | 6236.69 | 6621.5  | 62×95  | 悬空                                         |

| 122 | NC        | 6086.69 | 6621.5  | 62×95  | 悬空                                         |

| 123 | NC        | 5936.69 | 6621.5  | 62×95  | 悬空                                         |

| 124 | NC        | 5786.69 | 6621.5  | 62×95  | 悬空                                         |

| 125 | NC        | 5636.69 | 6621.5  | 62×95  | 悬空                                         |

| 126 | VDD33     | 5486.69 | 6621.5  | 62×95  | 波控电路 3.3V 电源                               |

| 127 | WR_MTP    | 5336.69 | 6621.5  | 62×95  | 输出, 写 MTP 使能, 不用时悬空                        |

| 128 | CLK_EE    | 5186.69 | 6621.5  | 62×95  | 输出, EEPROM/MTP 系统时钟, 不用时悬空                 |

| 129 | WR_EE     | 5036.69 | 6621.5  | 62×95  | 输出, 写 EEPROM 使能, 不用时悬空                     |

| 130 | RD_UPDATE | 4886.69 | 6621.5  | 62×95  | 输出, EEPROM/MTP 读使能, 不用时悬空                  |

| 131 | EEIN      | 4736.69 | 6621.5  | 62×95  | 输入, EEPROM/MTP 串行数据输入, 弱下拉, 不用时接地          |

| 132 | EEEN      | 4586.69 | 6621.5  | 62×95  | 输入, EEPROM/MTP 串行数据输入使能, 弱上拉, 不用时接 3.3V 电源 |

| 133 | EEOOUT    | 4436.69 | 6621.5  | 62×95  | 输出, EEPROM/MTP 串行输出, 弱上拉, 不用时悬空            |

| 134 | VDD33     | 4286.69 | 6621.5  | 62×95  | 波控电路 3.3V 电源                               |

| 135 | EEOE      | 4136.69 | 6621.5  | 62×95  | 输出, EEPROM/MTP 串行输出使能, 不用时悬空               |

| 136 | SPI_SEL   | 3986.69 | 6621.5  | 62×95  | SPI 模式选择控制, 弱下拉, 波控模式默认悬空态, 接高后为 SPI 控制模式  |

| 137 | DIN       | 3836.69 | 6621.5  | 62×95  | 串行信号输入, 弱下拉                                |

| 138 | DOUT      | 3686.69 | 6621.5  | 62×95  | 串行数据输出, 弱上拉                                |

| 139 | OE        | 3536.69 | 6621.5  | 62×95  | 输入, 波控输出使能, 弱下拉, 为低时输出有效                   |

| 140 | CLK       | 3386.69 | 6621.5  | 62×95  | 时钟输入, 弱下拉, 推荐 1~20MHz                      |

| 141 | DEN       | 3236.69 | 6621.5  | 62×95  | 输入, 串行数据使能, 弱上拉, 为低时输入有效                   |

| 142 | LD        | 3086.69 | 6621.5  | 62×95  | 自检控制信号, 弱下拉                                |

| 143 | FIN       | 2936.69 | 6621.5  | 62×95  | 功能寄存器串行输入, 弱上拉                             |

| 144 | FEN       | 2786.69 | 6621.5  | 62×95  | 输入, 功能寄存器使能, 弱上拉, 为低时 FIN 输入有效             |

| 145 | SET       | 2636.69 | 6621.5  | 62×95  | 三级寄存器锁存, 弱下拉                               |

|     |         |         |        |       |                                          |

|-----|---------|---------|--------|-------|------------------------------------------|

| 146 | TR1     | 2486.69 | 6621.5 | 62×95 | 输入, 波控输入控制信号, 弱下拉, 产生接收控制信号              |

| 147 | TR2     | 2336.69 | 6621.5 | 62×95 | 输入, 波控输入控制信号, 弱下拉, 产生脉冲发射控制信号            |

| 148 | VDD33   | 2186.69 | 6621.5 | 62×95 | 波控电路 3.3V 电源                             |

| 149 | TR3     | 2036.69 | 6621.5 | 62×95 | 输入, 波控输入控制信号, 弱下拉, 产生连续波发射控制信号, 不用时接地    |

| 150 | EN      | 1886.69 | 6621.5 | 62×95 | 输入, 波控使能, 弱下拉, 为低时波控有效                   |

| 151 | NC      | 1679.4  | 6604.4 | 74×74 | 悬空                                       |

| 152 | NC      | 1489.4  | 6604.4 | 74×74 | 悬空                                       |

| 153 | NC      | 1299.4  | 6604.4 | 74×74 | 悬空                                       |

| 154 | NC      | 1109.4  | 6604.4 | 74×74 | 悬空                                       |

| 155 | NC      | 919.4   | 6604.4 | 74×74 | 悬空                                       |

| 156 | VDD12   | 679.4   | 6604.4 | 74×74 | 波控电路内部 1.2V 电源, 建议外部接 0.1uF 稳压电容, 防止电磁干扰 |

| 157 | AC4_<3> | 569.4   | 6604.4 | 74×74 | 增益调节, 默认悬空, 接地时通道 4 增益调高 0.5dB           |

| 158 | AC4_<2> | 459.4   | 6604.4 | 74×74 | 增益调节, 默认悬空, 接地时通道 4 增益调低 1dB             |

| 159 | AC4_<1> | 349.4   | 6604.4 | 74×74 | 增益调节, 默认悬空, 接地时通道 4 增益调低 0.5dB           |

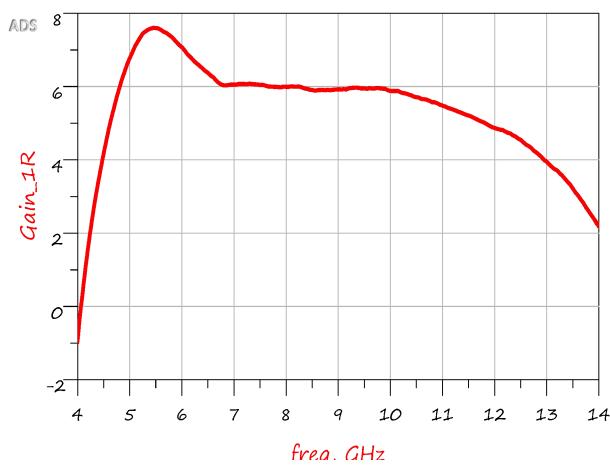

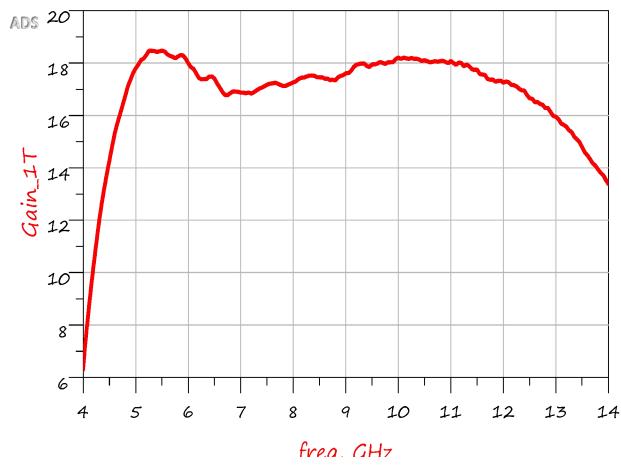

典型测试曲线 (如无特殊说明, 测试条件为电源 3.3V, 常温环境, 移相衰减基态)

### 小信号 S 参数

接收增益 (Rn 到 COM 口其他通道负载态)

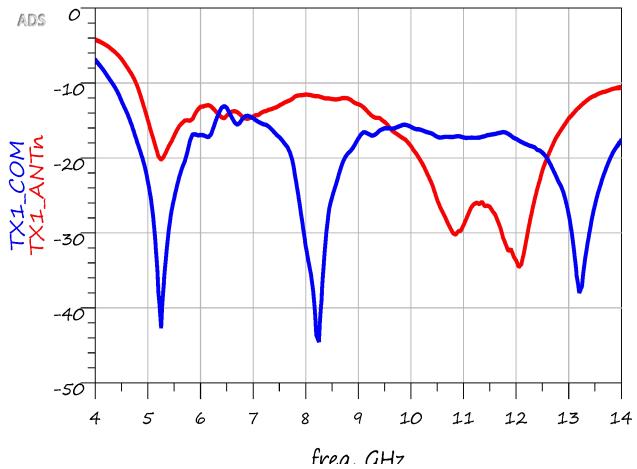

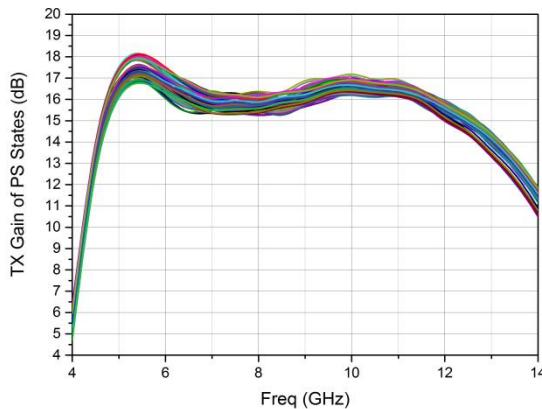

发射增益 (COM 到 Tn, 其他通道负载态)

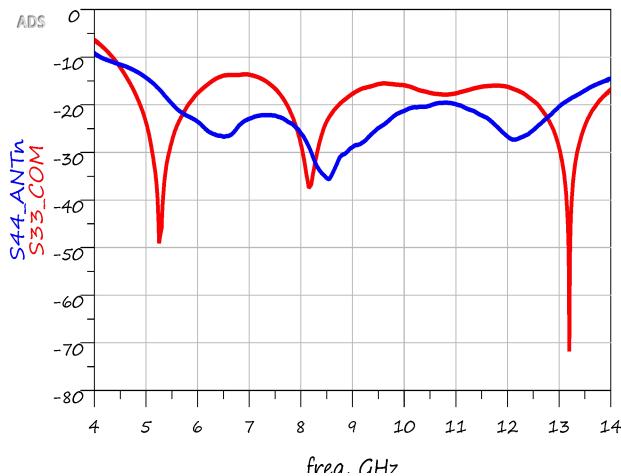

接收端口回波损耗

发射端口回波损

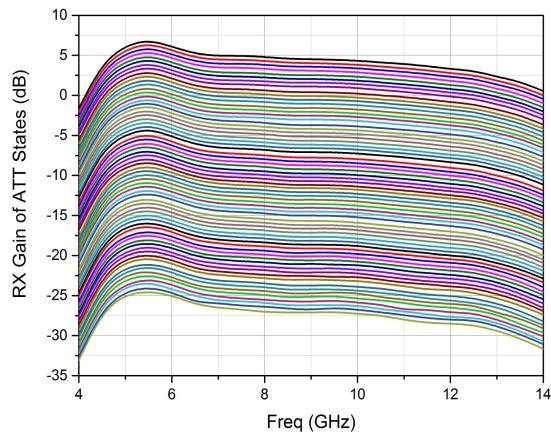

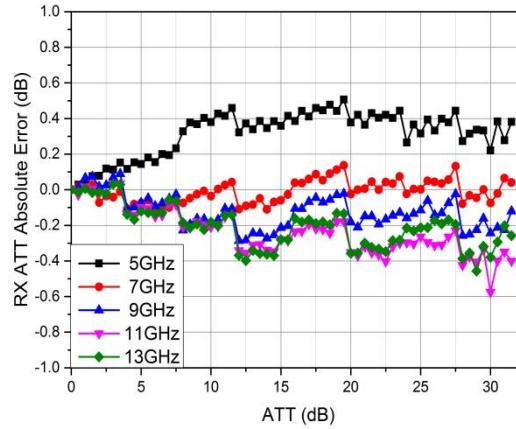

### 接收衰减性能

接收增益 64 态衰减曲线 vs 频率

接收模式衰减误差 vs 衰减值

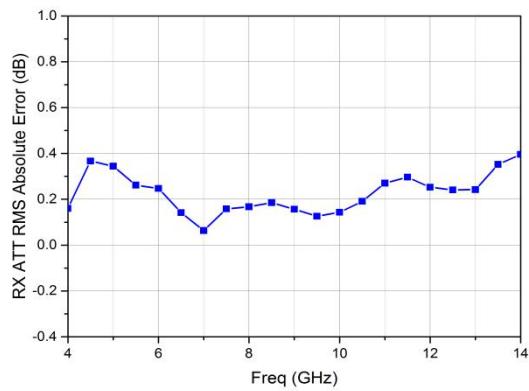

接收模式 RMS 衰减误差 vs 频率

接收模式 64 态衰减时附加相移 vs 频率

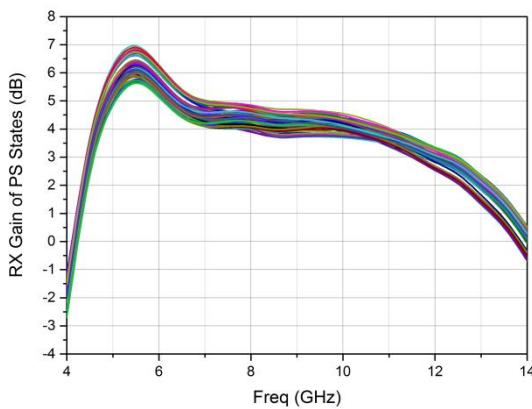

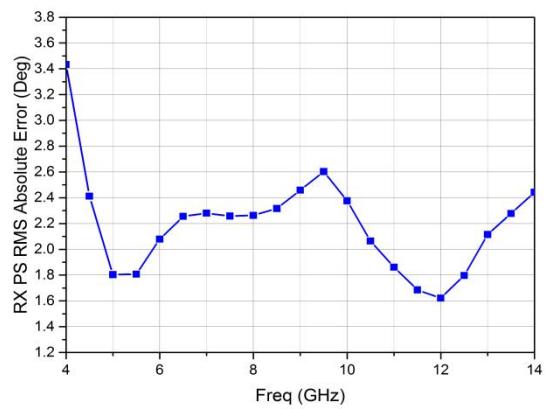

## 接收移相性能

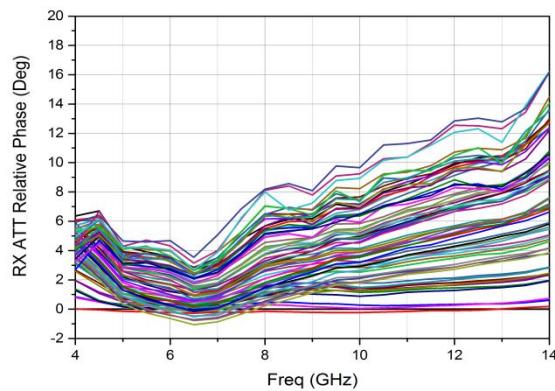

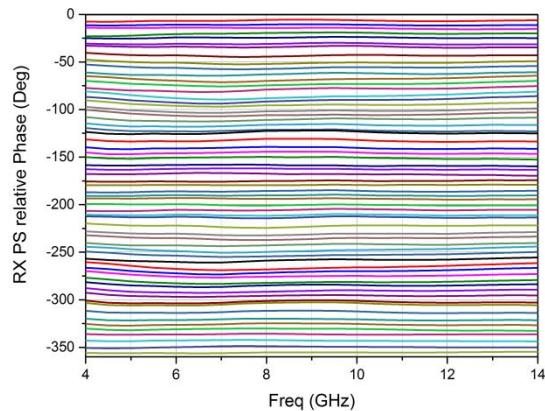

接收模式 64 状态相对移相曲线 vs 频率

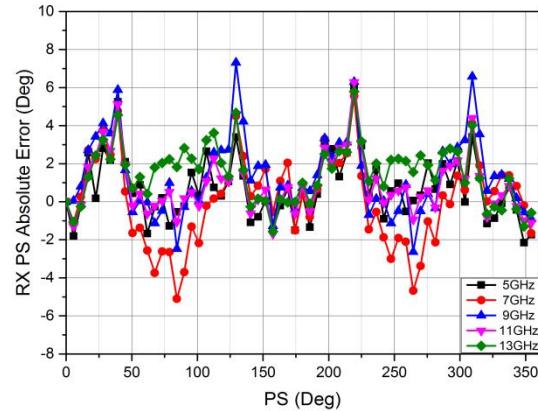

接收模式移相误差 vs 移相值

接收模式 64 状态移相时增益曲线 vs 频率

接收模式 RMS 移相误差 vs 频率

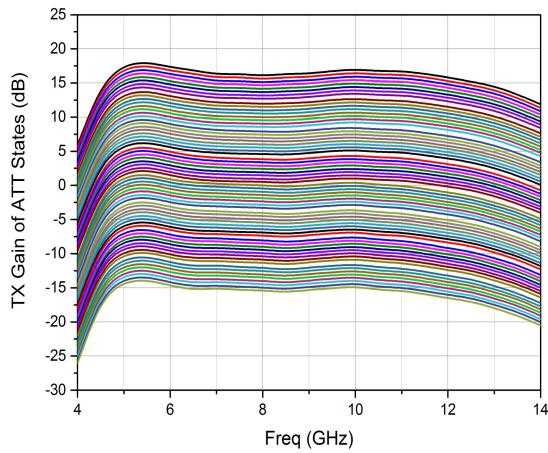

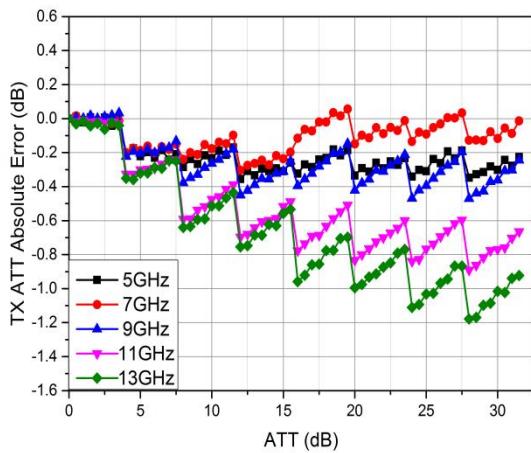

## 发射衰减性能

发射增益 64 状态衰减曲线 vs 频率

发射模式衰减误差 vs 衰减值

发射模式 RMS 衰减误差 vs 频率

发射模式 64 态衰减时附加相移 vs 频率

## 发射移相性能

发射模式 64 态相对移相曲线 vs 频率

发射模式移相误差 vs 移相值

发射模式 64 态移相时增益曲线 vs 频率

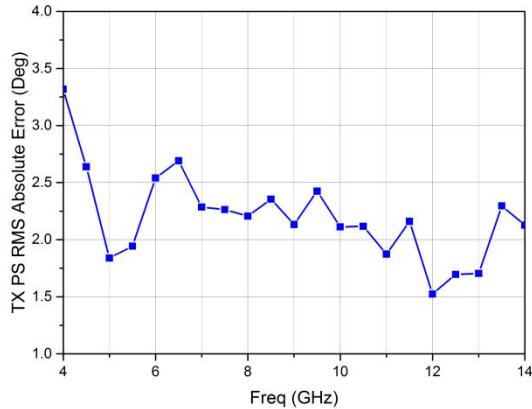

发射模式 RMS 移相误差 vs 频率

## 噪声与功率性能

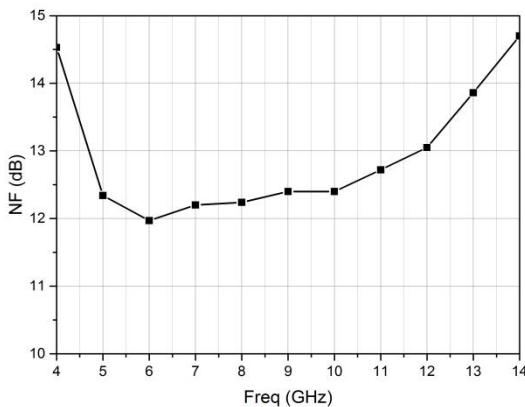

接收噪声系数 vs 频率

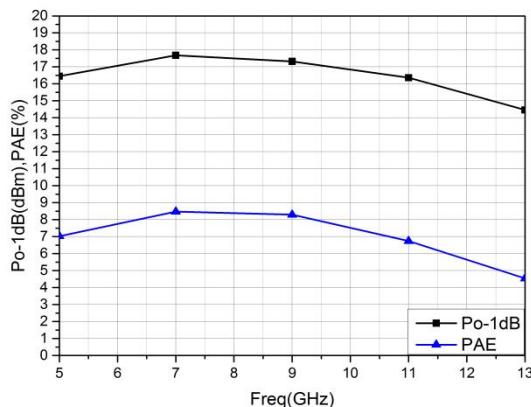

发射输出 1dB 功率、效率 vs 频率

## 数字波控功能

数字部分主要包括 5 个相同的控制通道和一个公共逻辑，5 个控制通道中包含 reg\_data1 模块，reg\_data2 模块，reg\_data3 模块，自检模块和开关控制逻辑；公共逻辑中包含 reg\_fun1 模块，reg\_fun2 模块，脉冲保护模块和温度保护模块。

### 单通道控制逻辑功能说明

外部引脚 SPI\_SEL 为低电平时为波控模式，SPI\_SEL 内部弱下拉。

#### 串行数据寄存器 reg\_data1

串行数据输入：当 DEN 为低，LD 为低，CLK 上升沿时，数据从 DIN 端口依次写入第 1 组寄存器的 reg\_data1[0]，每组寄存器 reg\_data1[25] 写入下一组 reg\_data1[0]；每组 reg\_data1 中原有数据依次从 reg\_data1[0] 移往 reg\_data1[25]；reg\_data1 的复位值为全 1。

串行数据输出：CLK 下降沿，数据从第 5 组 reg\_data1[25] 写入 reg\_dout 输出寄存器，reg\_dout 通过 DOUT 端口输出，DOUT 端口在 OE 为低时正常输出，OE 为高时输出高阻态；

串行自检数据加载：LD 为高，CLK 上升沿，将由 reg\_fun2[2][7:0] 寄存器指定的自检数据写入串行寄存器 reg\_data1。

#### 串行数据寄存器 reg\_data2

数据选择输入：在 DEN 的上升沿后三个周期，当 cal\_en 为高电平时（默认值为 1'b1）将串行数据寄存器（reg\_data1）中的数据写入功能寄存器 reg\_fun2[0][4:0] 选定的二级数据寄存器（reg\_data2），reg\_data2 的复位值为全 1。

YCC72-0513C1

数据手册

数据选择输出：在 SET 上升沿，将二级数据寄存器（reg\_data2）进行 32:1mux 输出，根据功能寄存器 reg\_fun2[1][4:0]选定的一组数据写入三级数据寄存器（reg\_data3）； reg\_data3 复位值全 1。

### 三级数据寄存器

reg\_data3[25:0]中数据定义

|     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| D25 | D24 | D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9  | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| AT5 | AT4 | AT3 | AT2 | AT1 | AT0 | MCT | MCR | AR5 | AR4 | AR3 | AR2 | AR1 | AR0 | PT5 | PT4 | PT3 | PT2 | PT1 | PT0 | PR5 | PR4 | PR3 | PR2 | PR1 | PR0 |

### PH 和 ATT 功能控制输出

#### 移相及衰减控制

| 输入  | 输出      |          | 状态  |

|-----|---------|----------|-----|

| TR1 | PH[5:0] | ATT[5:0] |     |

| 1   | PT[5:0] | AT[5:0]  | 发射态 |

| 0   | PR[5:0] | AR[5:0]  | 接收态 |

### 开关控制输出

收发状态控制，五个通道采用相同的逻辑控制输入，由各个通道的收发状态控制位分别输出相应通道的状态。各通道的 RX、TX0、TX1、TX\_D 控制输出最终由焊盘引出，0 或 3.3V 控制输出，约 2mA 驱动能力。

根据外部输入的 tr1、tr3、en 和内部配置的 mct、mcr 信号，以及脉冲保护输出 ptr2 来决定输出的状态。

#### 状态控制说明

| 输入   |  |     |                 |     |     | 输出  |    |     |     | 对应通道状态 |        |

|------|--|-----|-----------------|-----|-----|-----|----|-----|-----|--------|--------|

| EN   |  | TR1 | PTR2 (脉冲保护逻辑输出) | TR3 | MCR | MCT | RX | TX0 | TX1 | TX_D   |        |

| 0    |  | 0   | 0               | 0   | 0   | x   | 0  | 0   | 0   | 0      | 接收态    |

| 0    |  | 1   | 0               | 0   | 0   | x   | 1  | 0   | 0   | 0      | 过渡态    |

| 0    |  | 1   | 1               | 0   | x   | 0   | 1  | 1   | 0   | 1      | 脉冲发射态  |

| 0    |  | 1   | 0               | 1   | x   | 0   | 1  | 0   | 1   | 1      | 连续波发射态 |

| 其它组合 |  |     |                 |     |     | 1   | 0  | 0   | 0   | 0      | 负载态    |

### 功能寄存器 reg\_fun1

串行数据输入：FEN 为低，CLK 上升沿，数据从 FIN 端口依次写入 reg\_fun1[0],reg\_fun1 中原有数据依次从 reg\_fun1[0]移往 reg\_fun1[11]，reg\_fun1 复位值为全 1。

### 功能寄存器 reg\_fun2

根据 reg\_fun1[11:8]确定的地址，在 FEN 的上升沿后三个周期将 reg\_fun1[7:0]数据写入 reg\_fun2 寄存器指定位置。

功能寄存器说明如下表所列，表中功能寄存器组字节高低位与内部功能寄存器位定义高低顺序一致。

**功能寄存器说明**

| 序号 | 寄存器名            | 初始值          | 备注                                                                                           |

|----|-----------------|--------------|----------------------------------------------------------------------------------------------|

| 1  | reg_fun2[0]     | 8'hff        | reg_fun2[0][4:0]二级数据缓存 reg_data2 寄存器组写入地址                                                    |

| 2  | reg_fun2[1]     | 8'hff        | reg_fun2[1][4:0] 二级数据缓存 reg_data2 寄存器组输出地址                                                   |

| 3  | reg_fun2[2]     | 8'hff        | reg_fun2[3][7:0] 串行输出自检数据加载选择地址                                                              |

| 4  | reg_fun2[3]     | 8'hff        | reg_fun2[3][4:0]脉宽保护有效每个通道 1bit, 可单独打开、关闭保护功能                                                |

| 5  | reg_fun2[4]     | 8'h2         | 累加数 pro_add[7:0]<br>递减数 pro_dec[7:0]                                                         |

| 6  | reg_fun2[5]     | 8'h1         |                                                                                              |

| 7  | reg_fun2[6]     | 8'h68        | 缺省保护门限<br>205μs(4MHz)                                                                        |

| 8  | reg_fun2[7]     | 8'h6         |                                                                                              |

| 9  | reg_fun2[8]     | 8'h0         |                                                                                              |

| 10 | reg_fun2[9]     | 8'h0         |                                                                                              |

| 11 | reg_fun2[10]    | 8'hff        | 温度传感器使能打开, 温度保护使能打开、保护门限 6'h3F                                                               |

| 12 | reg_fun2[11]    | 8'hff        | 温度保护状态标志, 温度传感器反馈温度 6 位                                                                      |

| 13 | reg_fun2[12]    | 8'h02        | reg_fun2[12][7:6]读 MTP 高 2 位地址, reg_fun2[12][0]读写 MTP/EEPROM 使能, reg_fun2[12][1]补偿使能(cal_en) |

| 14 | reg_fun2[13]    | 8'h00        | 读 MTP 低 8 位地址                                                                                |

| 15 | reg_fun2[14]    | 0x01         | 硬件版本低位(初始版本号, 芯片升级版本号增加)                                                                     |

| 16 | reg_fun2[15]    | 8'h10        | 硬件版本高位美辰 8'h10                                                                               |

| 17 | reg_data1       | 26'h3fffffff |                                                                                              |

| 18 | reg_data2[31:0] | 26'h3fffffff |                                                                                              |

| 19 | reg_data3       | 26'h3fffffff |                                                                                              |

| 20 | pro_cnt         | 32'h0        |                                                                                              |

| 21 | pro_out         | 5'h0         |                                                                                              |

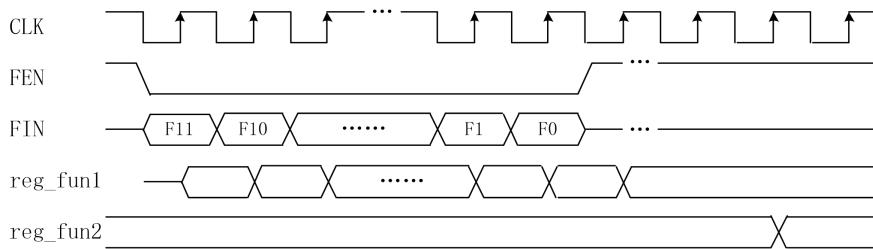

**波控时序要求**

**功能寄存器输入时序**

**功能寄存器输入时序**

FEN 为低时，时钟上升沿采样 FIN，内部将其串转并到 reg\_fun1[11:0]，在 FEN 的上升沿后三个周期将 reg\_fun1[7:0] 存入二级功能寄存器 reg\_fun2，存的地址由 reg\_fun1[11:8] 决定。

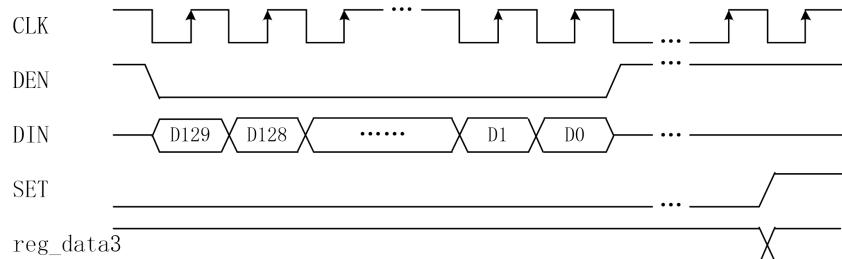

### 串行数据寄存器输入时序

串行数据输入时序

DEN 为低时，时钟上升沿采样 DIN，内部将其串转并到 reg\_data1[25:0]，在 DEN 的上升沿将 reg\_data1 存入二级数据存储区，存的地址由功能寄存器 reg\_fun2[0] 决定，默认为地址 31。在 DEN 拉高后至少 3 个周期后拉高 SET 信号，在 SET 上升沿将二级数据存储区的某一地址的数据更新到 reg\_data3，该地址由 reg\_fun2[1] 决定，默认为地址 31。

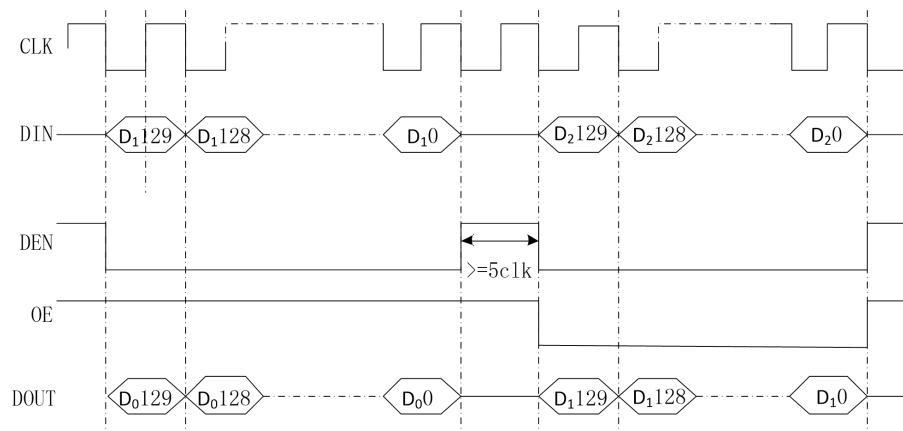

### 串行数据寄存器输出时序

串行数据输出时序

连续输入时，将 OE 拉低，DOUT 将依次输出上一次输入的 130bit 数据，可用于芯片级联场景。

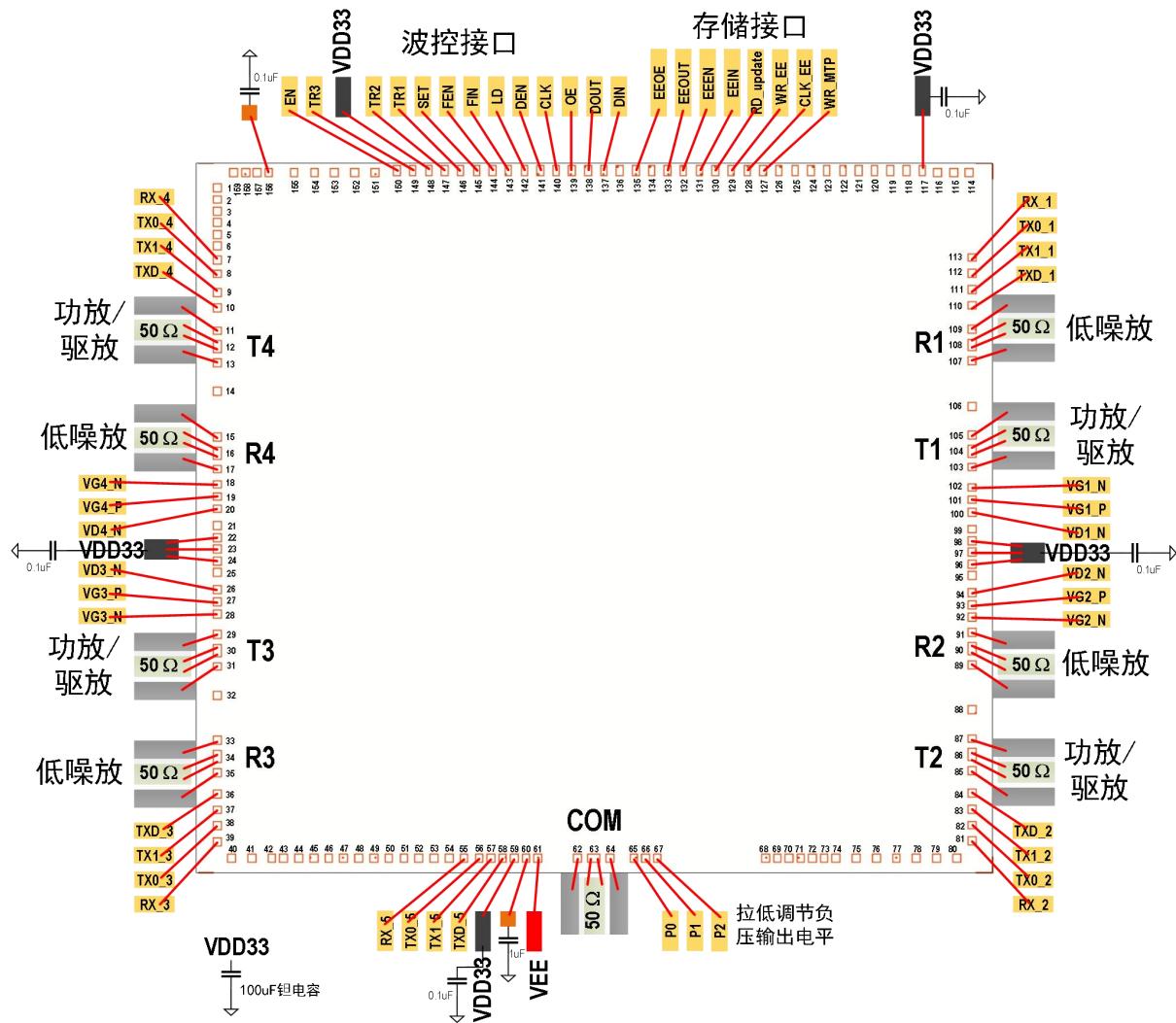

## 典型应用和装配示意图

下图所示为 YCC72-0513C1 芯片的应用电路和装配示意图。

各通道的射频端口和公共端口需要键合两根金丝到板上 50 欧姆传输线，金丝长度尽可能短，同时射频端口两侧 GND 焊盘最好 Downbond 到信号两侧的地，提高射频性能和端口隔离度，射频端口无需片外隔直。

本芯片的电源电压为 3.3V，应用时靠近芯片的电源焊盘处放置 0.1uF 贴片电容到地，此外，本四通道芯片需要至少 100uF 的钽电容滤波，用来降低脉冲切换时芯片端电源电压的波动。

芯片工作时，需先给电源端口 VDD33 上电，再给波控 I/O 口控制信号。

典型应用和装配示意图