# YFEN 論事电子

# YPM14-2118SC1

# 单路高压大电流调制电路 数据手册

四川益丰电子科技有限公司

Sichuan YiFeng Electronic Science & Technology Co., LTD

#### 1. 简述

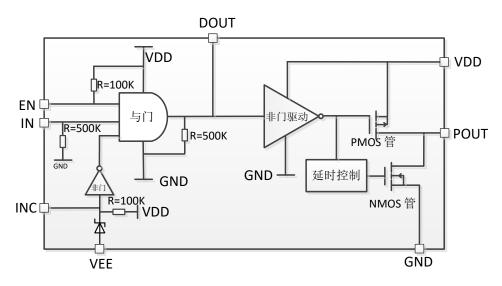

本电路是一款单路高压大电流电源调制电路,输入与输出为同向逻辑。本电路内部集成与门、驱动、 PMOS 管、泄放和负电监测等功能,最大工作电压 10V, PMOS 管最大输出电流 1.2A。

## 2. 功能

#### 2.1 原理框图

图 1 原理框图

#### 2.2 产品型号

表1产品型号对照表

| 产品型号          | 封装形式 | 质量等级 | 详细规范号        |

|---------------|------|------|--------------|

| YPM14-2118SC1 | 裸芯片  | 企军标  | ZG2118D-2023 |

### 3. 电性能

传真: 028 61962738

#### 3.1 绝对最大额定值

电话: 028 61962718 & 61962728

成都市青羊区敬业路 218 号 K 区 7 栋 201 室 610091

邮箱: sales@yifengelectronics.com 网址: www.yifengelectronics.com

#### 表 2 绝对最大额定值

| 参数               | 名称         | 最小值  | 最大值 | 单位                   |

|------------------|------------|------|-----|----------------------|

| IN/EN            | 芯片控制信号输入引脚 | -0.3 | 7   | V                    |

| VDD              | 芯片电源       | -0.3 | 12  | V                    |

| VEE              | 负压监测端      | -7   | 0.3 | V                    |

| $T_{\mathrm{J}}$ | 芯片结温度      |      | 150 | $^{\circ}\mathbb{C}$ |

| Ts               | 芯片贮存温度     | -65  | 150 | $^{\circ}$ C         |

# 3.2 电气特性 (T<sub>A</sub>=25℃)

#### 表 3 电气特性

| 参数                                      | 名称                   | 测试条件                                              | 最小值  | 典型值  | 最大值  | 单位 |

|-----------------------------------------|----------------------|---------------------------------------------------|------|------|------|----|

| VDD                                     | 芯片供电电压               |                                                   | 5    | 8    | 10   | V  |

| $I_s$                                   | 芯片静态电流               | VEE/IN/EN/DOUT/POUT<br>端悬空                        |      | 1.0  | 2.0  | mA |

| ${ m I}_{	exttt{DD}}$                   | 芯片动态电流               | IN 输入 5V 的<br>TTL, f=100kHz,输出<br>空载              |      | 1.5  | 2.0  | mA |

|                                         |                      | IN 输入 5V 的<br>TTL, f=1MHz,输出空<br>载                |      | 10   | 20   | mA |

| $I_{\mathrm{IHIN}}$                     | IN 输入端漏电流            | IN=5V                                             |      | 10   | 20   | uA |

| $I_{\scriptscriptstyle \rm ILIN}$       | IN 输入端漏电流            | IN=OA                                             |      | 1    | 10   | uA |

| $I_{	ext{IHEN}}$                        | EN 输入端漏电流            | EN=5V                                             | -50  | -30  |      | uA |

| $I_{\scriptscriptstyle \rm ILEN}$       | EN 输入端漏电流            | EN=OV                                             | -100 | -80  |      | uA |

| $V_{\scriptscriptstyle \mathrm{IL}}$    | IN/EN 输入低电平翻<br>转阈值  |                                                   | 0.8  | 1.8  |      | V  |

| $V_{\mathrm{IH}}$                       | IN/EN 输入高电平翻<br>转阈值  |                                                   |      | 2. 2 | 3.0  | V  |

| $V_{\text{ILVEE}}$                      | VEE 端口低电平翻转<br>阈值    | INC 悬空                                            | -4.3 | -4.0 |      | V  |

| $V_{\scriptscriptstyle \mathrm{IHVEE}}$ | VEE 端口高电平翻转<br>阈值    | INC 悬空                                            | -    | -3.7 | -3.2 | V  |

| ${ m I}_{	ext{	ext{VEE}}}$              | VEE 端口漏电流            | VDD=8V, VEE=-5V                                   |      | -240 |      | uA |

| $V_{	ext{OHD}}$                         | DOUT 端输出高电平<br>电压    | $C_L=10 \mathrm{pF}$ , $R_L=10 \mathrm{k} \Omega$ | 4. 7 | 4.8  |      | V  |

| $V_{OLD}$                               | DOUT 端输出低电平<br>电压    | $C_L$ =10pF, $R_L$ =10k $\Omega$                  |      | 0. 1 | 0.2  | V  |

| TR_DOUT                                 | DOUT 端输出上升沿          | $C_L=10pF$ , $R_L=10k\Omega$                      |      | 20   | 30   | ns |

| TF_DOUT                                 | DOUT 端输出下降沿          | $C_L=10pF$ , $R_L=10k\Omega$                      |      | 10   | 15   | ns |

| TDR_DOUT                                | DOUT 端输入至输出<br>上升沿延时 | $C_L$ =10pF, $R_L$ =10k $\Omega$                  |      | 25   | 40   | ns |

电话: 028 61962718 & 61962728

四川益丰电子科技有限公司

传真: 028 61962738

成都市青羊区敬业路 218 号 K 区 7 栋 201 室 610091

邮箱: sales@yifengelectronics.com 网址: www.yifengelectronics.com

| TDF_DOUT                   | DOUT 端输入至输出<br>下降沿延时 | $C_L$ =10pF, $R_L$ =10k $\Omega$   |     | 25   | 40  | ns |

|----------------------------|----------------------|------------------------------------|-----|------|-----|----|

| $V_{\mathrm{OHP}}$         | POUT 端输出高电平<br>电压    | VDD=8V, $R_L$ =12 $\Omega$         | 7.8 | 7.85 |     | V  |

| R <sub>OLN</sub>           | NMOS 管导通时的内阻         | IN=EN=OV, I <sub>OUT</sub> =-100mA |     | 4    | 8   | Ω  |

| $T_R$                      | POUT 输出上升沿           | $C_L=200 pF$ , $R_L=12 \Omega$     |     | 20   | 30  | ns |

| $T_{\scriptscriptstyle F}$ | POUT 输出下降沿           | $C_L$ =200pF, $R_L$ =12 $\Omega$   |     | 10   | 20  | ns |

| $T_{	ext{DR}}$             | POUT 端输入至输出<br>上升沿延时 | $C_L$ =200pF, $R_L$ =12 $\Omega$   |     | 28   | 40  | ns |

| $T_{	ext{DF}}$             | POUT 端输入至输出<br>下降沿延时 | $C_L$ =200pF, $R_L$ =12 $\Omega$   |     | 25   | 35  | ns |

| $T_{	ext{DR\_VEE}}$        | VEE 端输入至输出上<br>升沿延时  | $C_L$ =200pF, $R_L$ =12 $\Omega$   |     | 420  | 500 | nS |

| $T_{	ext{DF\_VEE}}$        | VEE 端输入至输出下<br>降沿延时  | $C_L$ =200pF, $R_L$ =12 $\Omega$   |     | 60   | 100 | nS |

# 4. 裸芯片引脚及尺寸

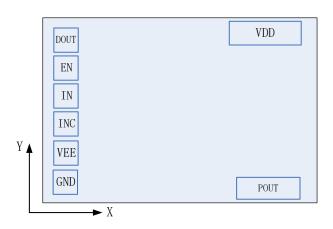

#### 4.1 裸芯片概貌图

图 2 裸芯片概貌图

说明: 1) 芯片不含划片槽尺寸 X=1550±30um, Y=950±30um;

- 2) 芯片不含划片槽尺寸 X=1590±50um, Y=990±50um;

- 3) 芯片厚度: 200±30um;

- 4) 划片槽尺寸: 80um;

- 5) VDD/POUT 的 PAD 尺寸: 90um\*250um, 其余所有 PAD 尺寸: 90um\*90um;

- 6) 键合方式: 建议采用 25um 金丝球焊;

- 7) 芯片背面为硅, 电极为 GND, 建议用导电胶粘剂到 GND。

电话: 028 61962718 & 61962728

传真: 028 61962738

四川益丰电子科技有限公司

成都市青羊区敬业路 218 号 K 区 7 栋 201 室 610091

邮箱: sales@yifengelectronics.com

网址: www.yifengelectronics.com

# 4.2 裸芯片引脚定义

表 4 裸芯片引脚定义

| 序号 | 名称   | PAD 中心坐标<br>(X,Y)<br>(单位: um) | 引脚说明                                                   |

|----|------|-------------------------------|--------------------------------------------------------|

| 1  | DOUT | (152, 830)                    | 与门输出端口,为后端其他数字芯片提供控制<br>信号,内部集成 500k Ω 下拉电阻,不用时可悬<br>空 |

| 2  | EN   | (152, 688)                    | 与门输入端口,内部集成 100k Ω 上拉电阻,不用时可悬空                         |

| 3  | IN   | (152, 546)                    | 与门输入端口,内部集成 500k Ω 下拉电阻                                |

| 4  | INC  | (152, 404)                    | 负电监测使能控制端口,需要负电监测时该端口悬空,不需要负电监测时,该端口接 GND              |

| 5  | VEE  | (152, 262)                    | 负电监测输入端,接-5V,不用时可悬空                                    |

| 6  | GND  | (152, 120)                    | 芯片地                                                    |

| 7  | POUT | (980, 85)                     | PMOS 管的输出,接负载                                          |

| 8  | VDD  | (980, 865)                    | 芯片电源                                                   |